# Software Synthesis and Code Generation for Signal Processing Systems

Shuvra S. Bhattacharyya, Member, IEEE, Rainer Leupers, and Peter Marwedel, Member, IEEE

Abstract—The role of software is becoming increasingly important in the implementation of digital signal processing (DSP) applications. As this trend intensifies, and the complexity of applications escalates, we are seeing an increased need for automated tools to aid in the development of DSP software. This paper reviews the state-of-the-art in programming language and compiler technology for DSP software implementation. In particular, we review techniques for high-level block-diagram-based modeling of DSP applications; the translation of block-diagram specifications into efficient C programs using global target-in-dependent optimization techniques; and the compilation of C programs into streamlined machine code for programmable DSP processors using architecture-specific and retargetable back-end optimizations. We also point out important directions for further investigation.

*Index Terms*—Code generation, dataflow signal processing, retargetable compilation, software synthesis.

#### I. Introduction

LTHOUGH dedicated hardware can provide significant speed and power consumption advantages for signal processing applications [1], extensive programmability is becoming an increasingly desirable feature of implementation platforms for very large scale integration (VLSI) signal processing. The trend toward programmable platforms is fueled by tight time-to-market windows, which in turn result from intense competition among DSP product vendors, and from the rapid evolution of technology, which shrinks the life cycle of consumer products. As a result of short time-to-market windows, designers are often forced to begin architecture design and system implementation before the specification of a product is fully completed. For example, a portable communication product is often designed before the signal transmission standards under which it will operate are finalized, or before the full range of standards that will be supported by the product is agreed upon. In such an environment, late changes in the design cycle are mandatory. The need to quickly make such late changes requires the use of software. Furthermore, whether or not the product specification is fixed beforehand, software-based implementations using off-the-shelf processors

Manuscript received September 1999; revised May 2000. The work of S. S. Bhattacharyya was supported by the National Science Foundation under CA-REER MIP9734275 and by Northrop Grumman Corporatioin. The work of R. Leupers and P. Marwedel was supported by HP EESof of California. This paper was recommended by Associate Editor J. Chambers.

Publisher Item Identifier S 1057-7130(00)07765-X.

take significantly less verification effort compared to custom hardware solutions.

Although the flexibility offered by software is critical in DSP applications, the implementation of production quality DSP software is an extremely complex task. The complexity arises from the diversity of critical constraints that must be satisfied; typically, these constraints involve stringent requirements on metrics, such as latency, throughput, power consumption, code size, and data storage requirements. Additional constraints include the need to ensure key implementation properties, such as bounded memory requirements and deadlock-free operation. As a result, unlike developers of software for general-purpose platforms, DSP software developers routinely engage in meticulous tuning and simulation of program code at the assembly-language level.

Important industry-wide trends at both the programming language level and the processor architecture level have had a significant impact on the complexity of DSP software development. At the architectural level, a specialized class of microprocessors has evolved that is streamlined to the needs of DSP applications. These DSP-oriented processors, called programmable digital signal processors (PDSP's), employ a variety of special-purpose architectural features that support common DSP operations, such as digital filtering and fast Fourier transforms [2]–[4]. At the same time, they often exclude features of general purpose processors, such as extensive memory management support, that are not important for many DSP applications.

Due to various architectural irregularities in PDSP's, which are required for their exceptional cost/performance and power/performance tradeoffs [2], compiler techniques for general-purpose processors have proven to be inadequate for exploiting the power of PDSP architectures from high-level languages [5]. As a result, the code quality of high-level procedural language (such as C) compilers for PDSP's has been several hundreds of percent worse than manually written assembly language code [6], [55]. This situation has necessitated the widespread use of assembly-language coding, and tedious performance tuning, in DSP software development. However, in recent years, a significant research community has evolved that is centered around the development of compiler technology for PDSP's. This community has begun to narrow the gap between compiler-generated code and manually optimized code.

It is expected that innovative processor-specific compilation techniques for PDSP's will provide a significant productivity boost in DSP software development, since such techniques will allow us to take the step from assembly programming of PDSP's

S. S. Bhattacharyya is with the University of Maryland, Electrical and Computer Engineering Department and UMIACS, College Park, MD 20742 USA.

R. Leupers and P. Marwedel are with the Department of Computer Science 12, University of Dortmund, 44221 Dortmund, Germany.

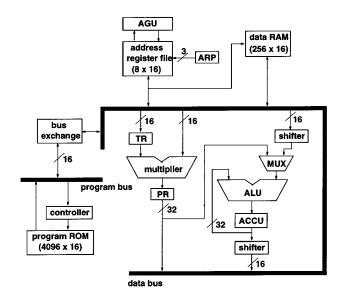

Fig. 1. Simplified architecture of Texas Instruments TMS320C25 DSP.

to the use of high-level programming languages. The key approach to reduce the overhead of compiler-generated code is the development of DSP-specific compiler optimization techniques. While classical compiler technology is often based on the assumption of a regular processor architecture, DSP-specific techniques are designed to be capable of exploiting the special architectural features of PDSP's. These include special-purpose registers in the data path, dedicated memory address-generation units, and a moderate degree of instruction-level parallelism.

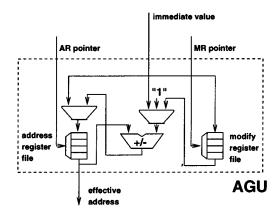

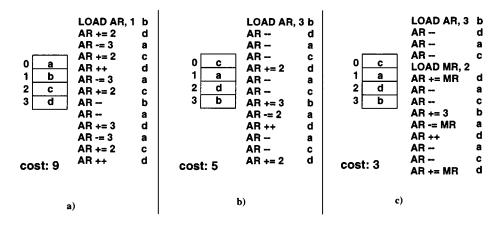

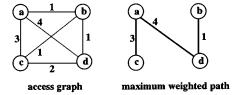

To illustrate this, consider the architecture of a popular fixed-point DSP (TI TMS320C25) in Fig. 1. Its data path comprises the registers TR, PR, and ACCU, each of which plays a specific role in communicating values between the functional units of the processor. This structure allows for a very efficient implementation of DSP algorithms (e.g. filtering algorithms). More regular architectures (e.g., with general-purpose registers) would, for instance, require more instruction bits for addressing the registers and more power for reading and writing the register file.

From a compiler viewpoint, the mapping of operations, program variables, and intermediate results to the data path in Fig. 1 must be done in such a way, that the amount of data transfer instructions between the registers is minimized. The address-generation unit (AGU) comprises a special arithmetic logic unit (ALU) and is capable of performing address arithmetic in parallel to the central data path. In particular, it provides parallel auto-increment instructions for address registers (ARs). As we will show later, exploitation of this feature in a compiler demands an appropriate memory layout of program variables. Besides the AGU, the data path also offers a certain degree of instruction-level parallelism. For instance, loading a memory value into register TR and accumulating a product stored in PR can be performed in parallel within a single machine instruction. Since such parallelism cannot be explicitly described in programming languages like C, compilers need to carefully schedule the generated machine instructions, so as to exploit the potential parallelism and to generate fast and dense code.

Further architectural features frequently present in PDSPs include parallel memory banks (providing higher memory-access

bandwidth), chained operations (such as multiply-accumulate), special arithmetic operations (such as addition with saturation), and mode registers (for switching between different arithmetic modes).

For most of the architectural features mentioned above, dedicated code-optimization techniques have recently been developed, an overview of which will be given in Section III. Many of these optimizations are computationally complex, resulting in a comparatively low compilation speed. This is intensified by the fact that compilers for PDSPs, besides the need for specific optimization techniques, have to deal with the phase coupling problem. The compilation process is traditionally divided into the phases of code selection, register allocation, and instruction scheduling, which have to be executed in a certain order. For all possible phase orders, the approach of separate compilation phases results in a code quality overhead, since each phase may impose obstructing constraints on subsequent phases, which would not have been necessary from a global viewpoint. While for regular processor architectures like RISCs this overhead is moderate and thus tolerable, it is typically much higher for irregular processor architectures as found in PDSPs. Therefore, it is desirable to perform the compilation phases in a coupled fashion, where the different phases mutually exchange information so as to achieve a global optimum.

Even though phase-coupled compiler techniques lead to a further increase in compilation time, it is widely agreed in the DSP software developer community that high compilation speed is of much lower concern than high code quality. Thus, compilation times of minutes or even hours may be perfectly acceptable in many cases. This fact gives good opportunities for novel computation-intensive approaches to compiling high level languages for PDSP's, which however would not be acceptable in general-purpose computing.

Besides pure code optimization issues, the large variety of PDSP's (both standard "off-the-shelf" processors and application specific processors) currently in use creates a problem of economic feasibility of compiler construction. Since code optimization techniques for PDSP's are highly architecture-specific by nature, a huge amount of different optimization techniques were required to build efficient compilers for all PDSP's available on the market. Therefore, in this paper we will also briefly discuss techniques for retargetable compilation. Retargetable compilers are capable of generating code not only for a single target processor, but for a class of processors, thereby reducing the number of compilers required. This is achieved by providing the compiler with a description of the machine for which code is to be generated, instead of hard-coding the machine description in the compiler. We will mention different approaches of processor modeling for retargetable compilation. Retargetability permits to quickly generate compilers for new processors. If the processor description formalism is flexible enough, then retargetable compilers may also assist in customizing an only partially predefined processor architecture for a given application.

At the system-specification level, the past several years have seen increased use of block-diagram-based graphical programming environments for digital signal processing. Such graphical programming environments, which enable DSP systems to be specified as hierarchies of block diagrams, offer several impor-

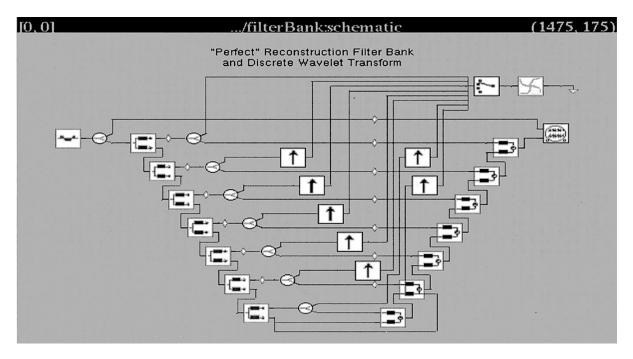

Fig. 2. Top-level block diagram specification of a discrete wavelet transform application implemented in Ptolemy [7].

tant advantages. Perhaps the most obvious of these advantages is their intuitive appeal. Although visual programming languages have seen limited use in many application domains, DSP system designers are used to thinking of systems in terms of graphical abstractions, such as signal flow diagrams, and thus, block-diagram specification via a graphical user interface is a convenient and natural programming interface for DSP design tools.

An illustration of a block diagram DSP system, developed using the Ptolemy design environment [7], is shown in Fig. 2. This is an implementation of a discrete wavelet transform [8] application. The top part of the figure shows the highest level of the block diagram specification hierarchy. Many of the blocks in the specification are *hierarchical*, which means that the internal functionality of the blocks are also specified as block diagrams ("nested" block diagrams). Blocks at the lowest level of the specification hierarchy, such as the individual FIR filters, are specified in a meta-C language (C augmented with special constructs for specifying block parameters and interface information).

In addition to offering intuitive appeal, the specification of systems in terms of connections between pre-defined encapsulated functional blocks naturally promotes desirable software engineering practices such as modularity and code reuse. As the complexity of applications continually increases while time-to-market pressures remain intense, reuse of design effort across multiple products is becoming more and more crucial to meeting development schedules.

In addition to their syntactic and software engineering appeal, there are a number of more technical advantages of graphical DSP tools. These advantages hinge on the use of appropriate models of computation to provide the precise underlying block diagram semantics. In particular, the use of *dataflow models* of computation can enable the application of powerful verification and synthesis techniques. Broadly speaking, dataflow modeling involves representing an application as a directed graph in

which the graph vertices represent computations, and edges represent logical communication channels between computations. Dataflow-based graphical specification formats are used widely in commercial DSP design tools, such as COSSAP by Synopsys, the Signal Processing Worksystem by Cadence, and the Advanced Design System by Hewlett–Packard. These three commercial tools all employ some form of the *synchronous dataflow (SDF)* model [9], the most popular variant of dataflow in existing DSP design tools. SDF specification allows bounded memory determination and deadlock detection to be performed comprehensively and efficiently at compile time. In contrast, both of these verification problems are in general impossible to solve (in finite time) for general purpose programming languages such as C.

Potentially the most useful benefit of dataflow-based graphical programming environments for DSP is that carefully specified graphical programs can expose the coarse-grain structure of the underlying algorithm, and this structure can be exploited to improve the quality of synthesized implementations in a wide variety of ways. For example, the process of scheduling—determining the order in which the computations in an application will execute—typically has a large impact on all of the key implementation metrics of a DSP system. A dataflow-based system specification exposes high-level scheduling flexibility that is often not possible to deduce manually or automatically from an assembly language or high-level procedural language specification. This scheduling flexibility can be exploited by a synthesis tool to streamline an implementation based on the given set of performance and cost constraints. We will elaborate on dataflow-based scheduling in Sections II-A-2 and II-B.

Although graphical dataflow-based programming tools for DSP have become increasingly popular in recent years, the use of these tools in industry is largely limited to simulation and prototyping. The quality of today's graphical programming tools is not sufficient to consistently deliver production-quality im-

plementations. As with procedural language compilation technology for PDSP's, synthesis from dataflow-based graphical specifications offers significant promise for the future, and is an important challenge confronting the DSP design and implementation research community today. Furthermore, these two forms of compiler technology are fully complementary to one another: the mixture of dataflow and C (or any other procedural language), as described in the example of Fig. 2, is an especially attractive specification format. In this format, coarsegrain "subprogram" interactions are specified in dataflow, while the functionality of individual subprograms is specified in C. Thus, dataflow synthesis techniques optimize the final implementation at the inter-subprogram level, while C compiler technology is required to perform fine-grained optimization within subprograms.

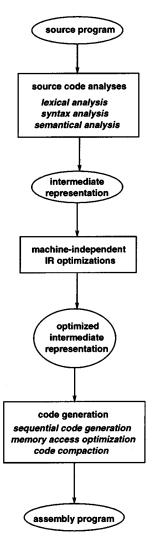

This paper motivates the problem of compiler technology development for DSP software implementation, provides a tutorial overview of modeling and optimization issues that are involved in the compilation of DSP software, and provides a review of techniques that have been developed by various researchers to address some of these issues. The first part of our overview focuses on coarse-grain software modeling and optimization issues pertinent to the compilation of graphical dataflow programs, and the second part focuses on fine-grained issues that arise in the compilation of high-level procedural languages such as C.

These two levels of compiler technology (coarse and fine grain) are commonly referred to as *software synthesis* and *code generation*, respectively. More specifically, by software synthesis, we mean the automated derivation of a software implementation (application program) in some programming language given a library of subprogram modules, a subset of selected modules from this library, and a specification of how these selected modules interact to implement the target application. Fig. 2 is an example of a program specification that is suitable for software synthesis. Here, SDF semantics are used to specify subprogram interactions. In Section II-B, we explore software synthesis issues for DSP.

On the other hand, code generation refers to the mapping of a software implementation in some programming language to an equivalent machine program for a specific programmable processor. Thus, the mapping of a C program on to the specific resources of the datapath in Fig. 1 is an example of code generation. We explore DSP code-generation technology in Section III.

## II. COMPILATION OF DATAFLOW PROGRAMS TO APPLICATION PROGRAMS

#### A. Dataflow Modeling of DSP Systems

To perform simulation, formal verification, or any kind of compilation from block-diagram DSP specifications, a precise set of semantics is needed that defines the interactions between different computational blocks in a specification. Dataflow-based computational models have proven to provide block-diagram semantics that are both intuitive to DSP system designers, and efficient from the point of view of verification and synthesis.

In the dataflow paradigm, a computational specification is represented as a directed graph. Vertices in the graph (called *actors*) correspond to the computational modules in the specification. In most dataflow-based DSP design environments, actors can be of arbitrary complexity. Typically, they range from elementary operations such as addition or multiplication to DSP subsystems such as FFT units or adaptive filters.

An edge  $(v_1, v_2)$  in a dataflow graph (DFG) represents the communication of data from  $v_1$  to  $v_2$ . More specifically, an edge represents a FIFO (first-in-first-out) queue that buffers data samples (tokens) as they pass from the output of one actor to the input of another. If  $e = (v_1, v_2)$  is a dataflow edge, we write  $src(e) = v_1$  and  $snk(e) = v_2$ . When DFGs are used to represent signal-processing applications, a dataflow edge e has a nonnegative integer delay del(e) associated with it. The delay of an edge gives the number of initial data values that are queued on the edge. Each unit of dataflow delay is functionally equivalent to the  $z^{-1}$  operator: the sequence of data values  $\{y_n\}$  generated at the input of the actor snk(e) is equal to the shifted sequence  $\{x_{n-del}(e)\}$ , where  $\{x_n\}$  is the data sequence generated at the output of the actor src(e).

1) Consistency: Under the dataflow model, an actor can execute at any time that it has sufficient data on all input edges. An attempt to execute an actor when this constraint is not satisfied is said to cause buffer underflow on all edges that do not contain sufficient data. For dataflow modeling to be useful for DSP systems, the execution of actors must also accommodate input data sequences of unbounded length. This is because DSP applications often involve operations that are applied repeatedly to samples in indefinitely long input signals. For an implementation of a dataflow specification to be practical, the execution of actors must be such that the number of tokens queued on each FIFO buffer (dataflow edge) remain bounded throughout the execution of the DFG. In other words, there should not be unbounded data accumulation on any edge in the DFG.

In summary, executing a dataflow specification of a DSP system involves two fundamental, processor-independent requirements: avoiding buffer underflow and avoiding unbounded data accumulation (buffering). The dataflow model imposes no further constraints on the sequence in which computations (actors) are executed. On the other hand, in procedural languages, such as C and FORTRAN, the ordering of statements as well as the use of control-flow constructs imply sequencing constraints beyond those that are required to satisfy data dependencies. By avoiding the overspecification of execution ordering, dataflow specifications provide synthesis tools with full flexibility to streamline the execution order to match the relevant implementation constraints and optimization objectives. This feature of dataflow is of critical importance for DSP implementation since, as we will see throughout the rest of this section, the execution order has a large impact on most important implementation metrics, such as performance, memory requirements, and power consumption.

The term "consistency" refers to the two essential requirements of DSP dataflow specifications—the absence of buffer underflow and unbounded data accumulation. We say that a *consistent* dataflow specification is one that can be implemented without any chance of buffer underflow or unbounded data ac-

cumulation (regardless of the input sequences that are applied to the system). If there exist one or more sets of infinite input sequences for which underflow and unbounded buffering can be avoided (by an appropriately-constructed implementation), and there also exist one or more sets for which underflow or unbounded buffering is inevitable, we say that a specification is *partially consistent*. A dataflow specification that is neither consistent nor partially consistent is called an *inconsistent specification*. More elaborate forms of consistency based on a probabilistic interpretation of token flow are explored in [10].

Clearly, consistency is a highly desirable property for DSP software implementation. For most consistent DFGs, tight bounds can be derived on the numbers of data values that coexist (data that has been produced but not yet consumed) on the individual edges (buffers). For such graphs, all buffer memory allocation can be performed statically, and thus, the overhead of dynamic memory allocation can be avoided entirely. This is a valuable feature when attempting to derive a streamlined software implementation.

2) Scheduling: A fundamental task in synthesizing software from an SDF specification is that of scheduling, which refers to the process of determining the order in which the actors will be executed. Scheduling is either dynamic or static. In static scheduling, the actor execution order is specified at synthesis time, and is fixed; in particular, the order is not data-dependent. To be useful in handling indefinitely long input data sequences, a static schedule must be periodic. A periodic, static schedule can be implemented in a finite amount of program memory space by encapsulating the program code for one period of the schedule within an infinite loop. Indeed, this is how such schedules are most often implemented in practice.

In dynamic scheduling, the sequence of actor executions (schedule) is not specified during synthesis, and run-time decision-making is required to ensure that actors are executed only when their respective input edges have sufficient data. Disadvantages of dynamic scheduling include the overhead (execution time and power consumption) of performing scheduling decisions at run-time, and decreased predictability, especially in determining whether or not any relevant real-time constraints will be satisfied. However, if the data production/consumption behavior of individual actors exhibits significant data-dependence, then dynamic scheduling may be required to avoid buffer underflow and unbounded data accumulation. Furthermore, if the performance characteristics of actors are impossible to estimate accurately, then effective dynamic scheduling leads to better performance by adaptively streamlining the schedule evolution to match the dynamic characteristics of the actors.

For many DSP applications, including the vast majority of applications that are amenable to the SDF model mentioned in Section I, actor behavior is highly predictable. For such applications, given the tight cost and power constraints that are typical of embedded DSP applications, it is highly desirable to avoid dynamic scheduling overhead as much as possible. The ultimate goal under such a high level of predictability is a (periodic) static schedule. If it is not possible to construct a static schedule, then it is desirable to identify "maximal" subsystems that can be scheduled statically, and use a small amount of dynamic decision-making to coordinate the execution of these

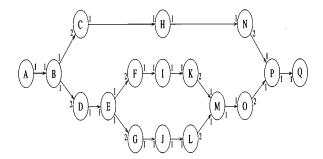

Fig. 3. Illustration of an explicit SDF specification.

statically-scheduled subsystems. Schedules that are constructed using such a hybrid, mostly-static approach are called *quasi-static schedules*.

3) SDF: A dataflow computation model can be viewed as a subclass of DFG specifications. A wide variety of dataflow computational models can be conceived depending on restrictions that are imposed on the manner in which dataflow actors consume and produce data. For example, SDF—which is the simplest and currently the most popular form of dataflow for DSP—imposes the restriction that the number of data values produced by an actor onto each output edge is constant, and similarly, the number of data values consumed by an actor from each input edge is constant. Thus, an SDF edge e has two additional attributes: the number of data values produced onto e by each invocation of the source actor, denoted prd(e), and the number of data values consumed from e by each invocation of the sink actor, denoted ens(e).

The example shown in Fig. 2 conforms to the SDF model. An SDF abstraction of a scaled down and simplified version of this system is shown in Fig. 3. Here, each edge is annotated with the number of data values produced and consumed by the source and sink actors, respectively. For example, prd((B,C))=1, and cns((B,C))=2.

The restrictions imposed by the SDF model offer a number of important advantages.

- Simplicity. Intuitively, when compared to more general types of dataflow actors, actors that produce and consume data in constant-sized packets are easier to understand, develop, interface to other actors, and maintain. This property is difficult to quantify; however, the rapid and extensive adoption of SDF in DSP design tools clearly indicates that designers can easily learn to think of functional specifications in terms of the SDF model.

- 2) Static scheduling and memory allocation. For SDF graphs, there is no need to resort to dynamic scheduling, or even quasi-static scheduling. For a consistent SDF graph, underflow and unbounded data accumulation can always be avoided with a periodic static schedule. Moreover, tight bounds on buffer occupancy can be computed efficiently. By avoiding the run-time overheads associated with dynamic scheduling and dynamic memory allocation, efficient SDF graph implementations offer significant advantages when cost, power, or performance constraints are severe.

- Consistency verification. A dataflow model of computation is a decidable dataflow model if it can be determined

in finite time, whether or not an arbitrary specification in the model is consistent. We say that a dataflow model is a *binary-consistency model* if every specification in the model is either consistent or inconsistent. In other words, a model is a binary-consistency model if it contains no partially consistent specifications. All of the decidable dataflow models that are used in practice today are binary-consistency models.

Binary consistency is convenient from a verification point of view since consistency becomes an inherent property of a specification: whether or not buffer underflow or unbounded data accumulation arises is not dependent on the input sequences that are applied. Of course, such convenience comes at the expense of restricted applicability. A binary-consistency model cannot be used to specify all applications.

The SDF model is a binary-consistency model, and efficient verification techniques exist for determining whether or not an SDF graph is consistent. Although SDF has limited expressive power in exchange for this verification efficiency, the model has proven to be of great practical value. SDF encompasses a broad and important class of signal processing and digital communications applications, including modems, multirate filter banks [8], and satellite receiver systems, just to name a few [9], [11], [12].

For SDF graphs, the mechanics of consistency verification are closely related to the mechanics of scheduling. The interrelated problems of verifying and scheduling SDF graphs are discussed in detail below.

4) Static Scheduling of SDF Graphs: The first step in constructing a static schedule for an SDF graph G=(V,E) is determining the number of times i(A) that each actor  $A\in V$  should be invoked in one period of the schedule. To ensure that the schedule period can be repeated indefinitely without unbounded data accumulation, the constraint

$$i(src(e))prd(e) = i(snk(e))cns(e)$$

, for every edge  $e \in E$

must be satisfied. The system of equations (1) is called the set of *balance equations* for G.

Clearly, a useful periodic schedule can be constructed only if the balance equations have a positive integer solution  $i^*$  ( $i^*(A) > 0$  for all  $A \in V$ ). Lee and Messerschmitt have shown that for a general SDF graph G, exactly one of the following conditions holds [9].

- The zero vector is the only solution to the balance equations

- 2) There exists a *minimal* positive integer solution q to the balance equations, and thus, every positive integer solution i' satisfies  $i'(A) \ge q(A)$  for all A. This minimal vector q is called the *repetitions vector* of G.

If the former condition holds, then G is inconsistent. Otherwise, a bounded buffer periodic schedule can be constructed provided that it is possible to construct a sequence of actor executions such that buffer underflow is avoided, and each actor A is executed exactly q(A) times. Given a consistent SDF graph,

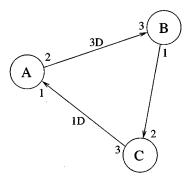

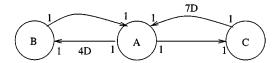

Fig. 4. A deadlocked SDF graph

we refer to an execution sequence that satisfies these two properties as a *valid schedule period*, or simply a *valid schedule*. Clearly, a bounded memory static schedule can be implemented in software by encapsulating the implementation of any valid schedule within an infinite loop.

A linear-time (O(|V|+|E|)) algorithm to determine whether or not a repetitions vector exists, and to compute a repetitions vector whenever one does exist can be found in [11].

For example, consider the SDF graph shown in Fig. 3. The repetitions vector components for this graph are given by

$$\begin{split} q(A) &= q(B) = q(P) = q(Q) = 4 \\ q(C) &= q(D) = q(E) = q(H) = q(M) = q(N) = q(O) = 2 \\ q(F) &= q(G) = q(I) = q(J) = q(K) = q(L) = 1. \end{split}$$

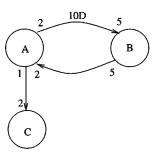

If a repetitions vector exists for an SDF graph, but a valid schedule does not exist, then the graph is said to be *deadlocked*. Thus, an SDF graph is consistent if and only if a repetitions vector exists, and the graph is not deadlocked. In general, whether or not a graph is deadlocked depends on the edge delays  $\{del(e)|e\in E\}$ , as well as the production and consumption parameters  $\{src(e)\}$  and  $\{snk(e)\}$ . An example of a deadlocked SDF graph is given in Fig. 4. An annotation of the form nD next to an edge in the figure represents a delay of n units. Note that the repetitions vector for this graph is given by

$$q(A) = 3, \quad q(B) = 2, \quad q(C) = 1.$$

(3)

Once a repetitions vector q has been computed, deadlock detection and the construction of a valid schedule can be performed concurrently. Premature termination of the scheduling procedure—termination before each actor A has been fully scheduled [scheduled q(A) times]—indicates deadlock. One simple approach is to schedule actor invocations one at a time and simulate the buffer activity in the DFG accordingly until all actors are fully scheduled. The buffer simulation is necessary to ensure that buffer overflow is avoided. A pseudocode specification of this simple approach can be found in [11]. Lee and Messerschmitt show that this approach terminates prematurely if and only if the input graph is deadlocked, and otherwise, regardless of the specific order in which actors are selected for scheduling, a valid schedule is always constructed [13].

In summary, SDF is currently the most widely used dataflow model in commercial and research-oriented DSP design tools. Commercial tools that employ SDF semantics include Simulink by The Math Works, SPW by Cadence, and HP Ptolemy by Hewlett Packard. SDF-based research tools include Gabriel [14], and several key domains in Ptolemy [7], from U.C. Berkeley; and ASSIGN from Carnegie Mellon [15]. The SDF model offers efficient verification of consistency for arbitrary specifications, and efficient construction of static schedules for all consistent specifications. Our discussion above outlined a simple, systematic technique for constructing a static schedule whenever one exists. In practice, however, it is preferable to employ more intricate scheduling strategies that take careful account of the costs (performance, memory consumption, etc.) of the generated schedules. In Section II-B, we will discuss techniques for streamlined scheduling of SDF graphs based on the constraints and optimization objectives of the targeted implementation. In the remainder of this section, we discuss a number of useful extensions to the SDF model.

5) Cyclo-Static Dataflow (CSDF): CSDF and scalable synchronout data flow (SSDF) (described in Section II-A-6) are presently the most widely used extensions of SDF. In CSDF, the number of tokens produced and consumed by an actor is allowed to vary as long the variation takes the form of a fixed periodic pattern [16], [17]. More precisely, each actor A in a CSDF graph has associated with it a fundamental period  $\tau(A) \in$  $\{1, 2, \ldots\}$ , which specifies the number of *phases* in one minimal period of the cyclic production/consumption pattern of A. For each input edge e to A, the scalar SDF attribute cns(e)is replaced by a  $\tau(A)$ -tuple  $C_{e,1}, C_{e,2}, \ldots, C_{e,\tau(A)}$ , where each  $C_{e,i}$  is a nonnegative integer that gives the number of data values consumed from e by A in the ith phase of each period of A. Similarly, for each output edge e, prd(e) is replaced by a  $\tau(A)$ -tuple  $P_{e,1}, P_{e,2}, \ldots, P_{e,\tau(A)}$ , which gives the numbers of data values produced in successive phases of A.

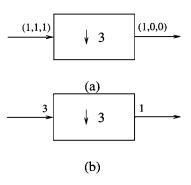

A simple example of a CSDF actor is illustrated in Fig. 5(a). This actor is a conventional downsampler actor (with downsampling factor 3) from multirate signal processing. Functionally, a downsampler performs the function y[i] = x[N(i-1)+1],where for k = 1, 2, ..., y[k] and x[k] denote the kth data values produced and consumed, respectively. Thus, for every input value that is copied to the output, N-1 input values are discarded. As shown in Fig. 5(b) for n=3, this functionality can be specified by a CSDF actor that has N phases. A data value is consumed on the input for all N phases, resulting in the N-component consumption tuple (1, 1, ..., 1); however, a data value is produced onto the output edge only on the first phase, resulting in the production tuple  $(1, 0, 0, \ldots, 0)$ .

Like SDF, CSDF is a binary consistency model, and it is possible to perform efficient verification of bounded memory requirements and buffer underflow avoidance for CSDF graphs [17]. Furthermore, static schedules can always be constructed for consistent CSDF graphs.

A CSDF actor A can easily be converted into an SDF actor A', such that if identical sequences of input data values are applied to A and A', then identical output data sequences result. Such a functionally equivalent SDF actor A' can be derived by having each invocation of A' implement one fundamental CSDF period of A (that is,  $\tau(A)$  successive phases of A). Thus, for each output edge e' of A', the SDF parameters of e' are given by:

Fig. 5. (a) CSDF and (b) SDF versions of a downsampler block.

1)

$$del(e') = del(e)$$

2)  $prd(e') = \sum_{i=1}^{\tau(A)} P_{e_i}$

1) del(e') = del(e)2)  $prd(e') = \sum_{i=1}^{\tau(A)} P_{e,i}$ and for each input edge, the delay is again given by 1) above, while the consumption parameter is given by

3)

$$cns(e') = \sum_{i=1}^{\tau(A)} C_{e,i}$$

3)  $cns(e') = \sum_{i=1}^{\tau(A)} C_{e,\,i}$  where e is the corresponding output or input edge of the CSDF actor A. Applying this conversion to the downsampler example discussed above gives an "SDF equivalent" downsampler that consumes a block of N input data values on each invocation, and produces a single data value, which is a copy of the first value in the input block. The SDF equivalent for Fig. 5(a) is illustrated in Fig. 5(b).

Since any CSDF actor can be converted to a functionally equivalent SDF actor, it follows that CSDF does not offer increased expressive power at the level of individual actor functionality (input-output mappings). However, the CSDF model can offer increased flexibility in compactly and efficiently representing interactions between actors.

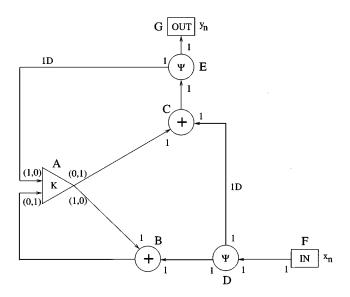

As an example of increased flexibility in expressing actor interactions, consider the CSDF specification illustrated in Fig. 6. This specification represents a recursive digital filter computation of the form

$$y_n = k^2 y_{n-1} + kx_n + xn - 1. (4)$$

In Fig. 6, the two-phase CSDF actor labeled A represents a scaling (multiplication) by the constant factor k. In each of its two phases, actor A consumes a data value from one of its input edges, multiplies the data value by k, and produces the resulting value onto one of its output edges. The CSDF specification of Fig. 6 thus exploits our ability to compute (4) using the equivalent formulation

$$y_n = k(ky_{n-1} + x_n) + xn - 1 \tag{5}$$

which requires only addition blocks and k-scaling blocks. Furthermore, the two k-scaling operations contained in (5) are consolidated into a single CSDF actor (actor A).

Such consolidation of distinct operations from different data streams offers two advantages. First, it leads to more compact representations since fewer vertices are required in the CSDF graph. For large or complex applications, this can result in more intuitive representations, and can reduce the time required to perform various analysis and synthesis tasks. Second, it allows a precise modeling of resource sharing decisions—pre-specified bindings of multiple operations in a DSP application

Fig. 6. An example that illustrates the compact modeling of resource sharing using CSDF. The actor labeled  $\Psi$  denotes a dataflow fork, which simply replicates its input tokens on all of its output edges. The lower portion of the figure gives a valid schedule for this CSDF specification. Here,  $A_1$  and  $A_2$  denote the first and second phases of the CSDF actor A.  $y_n = k^2 y_{n-1} + kx_n + x_{n-1} = k(ky_n + x_n) + x_{n-1}$ .

onto individual hardware resources (such as functional units) or software resources (such as subprograms)—within the framework of dataflow. Such pre-specified bindings may arise from constraints imposed by the designer, and from decisions taken during synthesis or design space exploration.

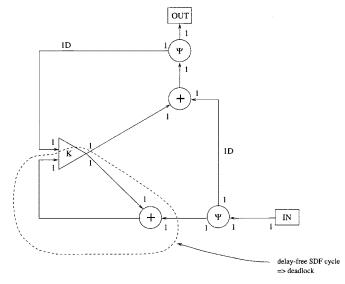

The ability to compactly and precisely model the sharing of actors in CSDF stems from the ability to selectively "turn off" data dependencies from arbitrary subsets of input edges in any given phase of an actor. In contrast, an SDF actor requires at least one data value on each input edge before it can be invoked. In the presence of feedback loops, this requirement may preclude a shared representation of an actor in SDF, even though it may be possible to achieve the desired sharing using a functionally equivalent CSDF actor. This is illustrated in Fig. 7, which is derived from the CSDF specification of Fig. 6 by replacing the "shared" CSDF actor with its functionally equivalent SDF counterpart. Since the graph of Fig. 7 contains a delay-free cycle, clearly we can conclude that the graph is deadlocked, and thus a valid schedule does not exist. In other words, this is an inconsistent dataflow specification. In contrast, it is easily verified that the schedule  $A_1FDBA_2CEG$  is a valid schedule for the CSDF specification of Fig. 6, where  $A_1$  and  $A_2$  denote the first and second phases of the CSDF actor A, respectively.

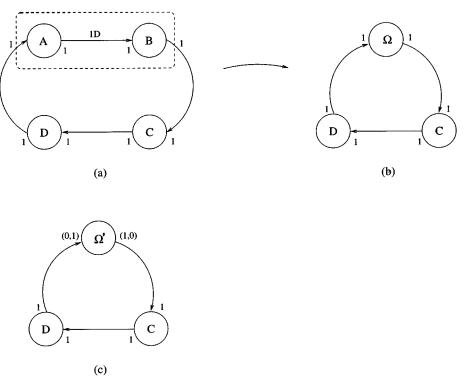

Similarly, an SDF model of a *hierarchical actor* may introduce deadlock in a system specification, and such deadlock can often be avoided by replacing the hierarchical SDF actor with a functionally equivalent hierarchical CSDF actor. Here, by a hierarchical SDF actor we mean an actor whose internal functionality is specified by an SDF graph. The utility of CSDF in constructing hierarchical specifications is illustrated in Fig. 8.

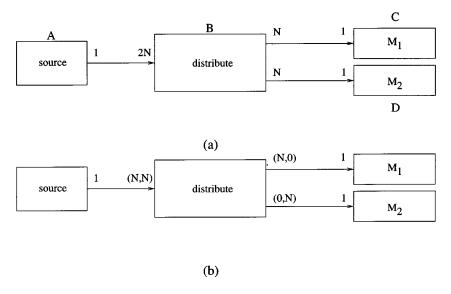

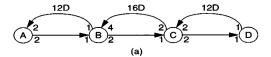

CSDF also offers decreased buffering requirements for some applications. An illustration is shown in Fig. 9. Fig. 9(a) depicts a system in which N-element blocks of data are alternately distributed from the data source to two processing modules  $M_1$

Fig. 7. SDF version of the specification in Fig. 6.

and  $M_2$ . The actor that performs the distribution is modeled as a two-phase CSDF actor that inputs an N-element data block on each phase, sends the input block to  $M_1$  in the first phase, and sends the input block to  $M_2$  in the second phase. It is easily seen that the CSDF specification of Fig. 9(a) can be implemented with a buffer of size N on each of the three edges. Thus, the total buffering requirement is 3N for this specification.

If we replace the CSDF "block-distributor" actor with its functionally equivalent SDF counterpart, then we obtain the pure SDF specification depicted in Fig. 9(b). The SDF version of the distributor must process two blocks at a time to conform to SDF semantics. As a result, the edge that connects the data source to the distributor requires a buffer of size 2N. Thus, the total buffering requirement of the SDF graph of Fig. 9(b) is 4N, which is 33% greater than the CSDF version of Fig. 9(a).

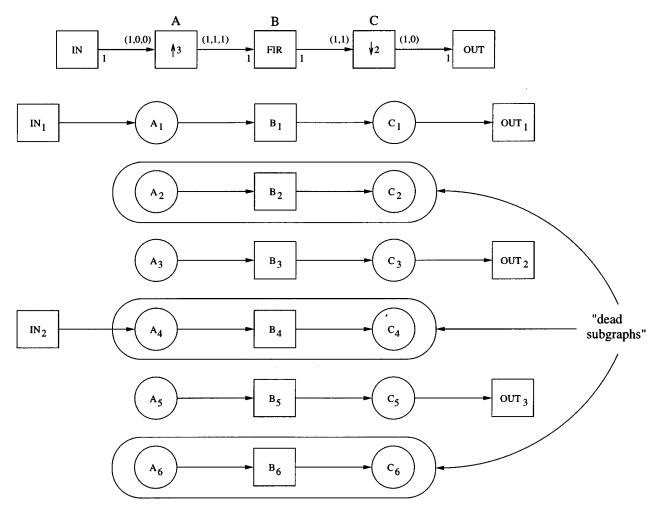

Yet another advantage offered by CSDF is that by decomposing actors into a finer level (phase level) of specification granularity, basic behavioral optimizations such as constant propagation and dead code elimination [18], [57] are facilitated significantly [19]. As a simple example of dead code elimination with CSDF, consider the CSDF specification shown in Fig. 10(a) of a multirate finite impulse response (FIR) filtering system that is expressed in terms of basic multirate building blocks. From this graph, the equivalent expanded homogeneous SDF graph, shown in Fig. 10(b), can be derived using concepts discussed in [9], [17]. In the expanded graph, each actor corresponds to a single phase of a CSDF actor or a single invocation of an SDF actor within a single period of a periodic schedule. From Fig. 10(b) it is apparent that the results of some computations (SDF invocations or CSDF phases) are never needed in the production of any of the system outputs. Such computations correspond to dead code and can be eliminated during synthesis without compromising correctness. For this example, the complete set of subgraphs that correspond to dead code is illustrated in Fig. 10(b). Parks, Pino, and Lee show that such "dead subgraphs" can be detected with a straightforward algorithm [19].

Fig. 8. An example that illustrates the utility of cyclo-static dataflow in constructing hierarchical specifications. (b) Grouping the actors A and B into the hierarchical SDF actor  $\Omega$  results in a deadlocked SDF graph. (c) In contrast, an appropriate CSDF model of the hierarchical grouping avoids deadlock; the two phases of the hierarchical CSDF actor  $\Omega'$  in (c) are specified by  $\Omega'_1: B. \Omega'_2: A.$  A valid schedule for the CSDF specification is  $\Omega'_1: CD\Omega'_2$ .

Fig. 9. An example of the use of CSDF to decrease buffering requirements.

In summary, CSDF is a useful generalization of SDF that maintains the properties of binary consistency, efficient verification, and static scheduling, while offering a more rich range of inter-actor communication patterns, improved support for hierarchical specifications, more economical data buffering, and improved support for basic behavioral optimizations. CSDF concepts are used in a number of commercial design tools such as *DSP Canvas* by Angeles Design Systems, and *Virtuoso Synchro* by Eonic Systems.

6) SSDF: The SSDF model is an extension of SDF that enables software synthesis of *vectorized* implementations, which

exploit the facility for efficient block processing in many DSP applications [20]. The internal (host language) specification of an SSDF actor A assumes that the actor will be executed in groups of  $N_v(A)$  successive invocations, which operate on  $(N_v(A)cns(e))$ -unit blocks of data at a time from each input edge e. Such block processing reduces the rate of inter-actor context switching and context switching between successive code segments within complex actors, and it also may improve execution efficiency significantly on deeply pipelined architectures. The vectorization parameter  $N_v$  of each SSDF actor invocation is selected carefully during synthesis. This

Fig. 10. Example of efficient dead-code elimination using CSDF.

selection should be based on constraints imposed by the SSDF graph structure, the memory constraints, and the performance requirements of the target application. Since the utility of SSDF is closely tied to optimized synthesis techniques, we defer detailed discussion of SSDF to Section II-B-4, which focuses on throughput-oriented optimization issues for software synthesis.

SSDF is a key specification model in the popular COSSAP design tool that was originally developed by Cadis and the Aachen University of Technology [21], and is now developed by Synopsys.

7) Other Dataflow Models: The SDF, CSDF, and SSDF models discussed above are all used in widely distributed DSP design tools. A number of more experimental DSP dataflow models have also been proposed in recent years. Although these models all offer additional insight on dataflow modeling for DSP, further research and development is required before the practical utility of these models is clearly understood. In the remainder of this section, we briefly review some of these experimental models.

The multidimensional synchronous dataflow model (MDSDF), proposed by Lee [22], and explored further by Murthy [23], extends SDF concepts to applications that operate on multidimensional signals, such as those arising in image and video processing. In MDSDF, each actor produces and consumes data in units of *n*-dimensional cubes, where *n* can

Fig. 11. Example of an MDSDF actor.

be arbitrary, and can differ from actor to actor. The "synchrony" requirement in MDSDF constrains each production and consumption n-cube to be of fixed size  $s_1 \times s_2 \times \ldots \times s_n$ , where each  $s_i$  is a constant. For example, an image processing actor that expands a  $512 \times 512$ -pixel image segment into a  $1024 \times 1024$  segment would have the MDSDF representation illustrated in Fig. 11.

We say that a dataflow computation model is *statically schedulable* if a static schedule can always be constructed for a consistent specification in the model. For SDF, CSDF, and MDSDF, binary consistency and static schedulability both hold. The well-behaved dataflow (WBDF) model [24], proposed by Gao, Govindarajan, and Panangaden, is an example of a binary-consistency model that is not statically schedulable. The WBDF model permits the use of a limited set of data-dependent control-flow constructs, and thus requires dynamic scheduling, in general. However, the use of these constructs is restricted in such a way that the inter-related properties of

binary consistency and efficient bounded memory verification are preserved, and the construction of efficient quasi-static schedules is facilitated.

The Boolean dataflow (BDF) model [25] is an example of a DSP dataflow model for which binary consistency does not hold. BDF introduces the concept of *control inputs*, which are actor inputs that affect the number of tokens produced and consumed at other input/output ports. In BDF, the values of control inputs are restricted to the set  $\{T, F\}$ . The number of tokens consumed by an actor from a noncontrol input edge, or produced onto an output edge is restricted to be constant, as in SDF, or a function of one or more data values consumed at control inputs. BDF attains greatly increased expressive power by allowing data-dependent production and consumption rates. In exchange, some of the intuitive simplicity and appeal of SDF is lost, static scheduling cannot always be employed, and the problems of bounded memory verification and deadlock detection become undecidable [26], which means that, in general, they cannot be solved in finite time. However, heuristics have been developed for constructing efficient quasi-static schedules, and attempting to verify bounded memory requirements. These heuristics have been shown to work well in practice [26]. A natural extension of BDF, called *integer-controlled dataflow*, that allows control tokens to take on arbitrary integer values has been explored in [27].

Parameterized dataflow [29], [28] provides a general framework for incorporating powerful dynamic reconfiguration capabilities into arbitrary dataflow models of computation, such as the models described above.

# B. Optimized Synthesis of DSP Software from Dataflow Specifications

In Section II-A, we reviewed several dataflow models for high-level block-diagram specification of DSP systems. Among these models, SDF and the closely related SSDF model are the most mature. In this section, we examine fundamental tradeoffs and algorithms involved in the synthesis of DSP software from SDF and SSDF graphs. Except for the vectorization approaches discussed in Section II-B-4, the techniques discussed in this section apply equally well to both SDF and SSDF. For clarity, we present these techniques uniformly in the context of SDF.

1) Threaded Implementation of DFGs: A software synthesis tools generates application programs by piecing together code modules from a predefined library of software building blocks. These code modules are defined in terms of the target language of the synthesis tool. Most SDF-based design systems use a model of synthesis called threading. Given an SDF representation of a block-diagram program specification, a threaded synthesis tool begins by constructing a periodic schedule. The synthesis tool then steps through the schedule and for each actor instance A that it encounters, it inserts the associated code module  $A_m$  from the given library (inline threading), or inserts a call to a subroutine that invokes  $A_m$ (subprogram threading). Threaded tools may employ purely inline threading, purely subroutine threading, or a mixture of inline and subprogram-based instantiation of actor functionality (hybrid threading). The sequence of code modules/subroutine calls that is generated from a DFG is processed by a buffer

Fig. 12. A simple example that we use to illustrate tradeoffs involved in compiling SDF specifications.

management phase that inserts the necessary target program statements to route data appropriately between actors.

2) Scheduling Tradeoffs: In this section, we provide a glimpse at the complex range of tradeoffs that are involved during the scheduling phase of the synthesis process. At present, we consider only inline threading. Subprogram and hybrid threading are considered in Section II-B-5. Synthesis techniques that pertain to SSDF, which are discussed in Section II-B-4, can be applied with similar effectiveness to inline, subprogram or hybrid threading.

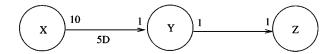

Scheduling is a critical task in the synthesis process. In a software implementation, scheduling has a large impact on key metrics such as program and data memory requirements, performance, and power consumption. Even for a simple SDF graph, the underlying range of tradeoffs may be very complex. For example, consider the SDF graph in Fig. 12. The repetitions vector components for this graph are q(X)=1, q(Y)=q(Z)=10. One possible schedule for this graph is given by

$$S_1 = YZYZYZYZYZYZYZYZYZYZYZ. (6)$$

This schedule exploits the additional scheduling flexibility offered by the delays placed on edge (X,Y). Recall that each delay results in an initial data value on the associated edge. Thus, in Fig. 12, five executions of Y can occur before X is invoked, which leads to a reduction in the amount of memory required for data buffering.

To discuss such reductions in buffering requirements precisely, we need a few definitions. Given a schedule, the *buffer size* of an SDF edge is the maximum number of *live tokens* (tokens that are produced but not yet consumed) that coexist on the edge throughout execution of the schedule. The *buffer requirement* of a schedule S, denoted buf(S), is the sum of the buffer sizes of all of the edges in the given SDF graph. For example, it is easily verified that  $buf(S_1) = 11$ .

The quantity buf(S) is the number of memory locations required to implement the dataflow buffers in the input SDF graph assuming that each buffer is mapped to a separate segment of memory. This is a natural and convenient model of buffer implementation. It is used in SDF design tools such as Cadence's SPW and the SDF-related code-generation domains of Ptolemy. Furthermore, scheduling techniques that employ this buffering model do not preclude the sharing of memory locations across multiple, noninterfering edges (edges whose lifetimes do not overlap): the resulting schedules can be post-processed by any general technique for array memory allocation, such as the well-known first-fit or best-fit algorithms. In this case, the scheduling techniques, which attempt to minimize the sum of the individual buffer sizes, employ a buffer-memory metric that is an upper bound approximation to the final buffer-memory cost.

One problem with the schedule  $S_1$  under the assumed inline threading model is that it consumes a relatively large amount of

program memory. If  $\kappa(A)$  denotes the code size (number of program memory words required) for an actor A, then the code-size cost of  $S_1$  can be expressed as  $\kappa(X) + 10\kappa(Y) + 10\kappa(Z)$ .

By exploiting the repetitive subsequences in the schedule to organize compact looping structures, we can reduce the code-size cost required for the actor execution sequence implemented by  $S_1$ . The structure of the resulting software implementation can be represented by the *looped schedule*

$$S_2 = (5YZ)X(5YZ). \tag{7}$$

Each parenthesized term  $(nT_1T_2...T_m)$  (called a *schedule loop*) in such a looped schedule represents the successive repetition n times of the invocation sequence  $T_1T_2...T_m$ . Each *iterand*  $T_i$  can be an instantiation (*appearance*) of an actor, or a looped subschedule. Thus, this notation naturally accommodates nested loops.

Given an arbitrary firing sequence F (that is, a schedule that contains no schedule loops), and a set of code-size costs for all of the given actors, a looped schedule can be derived that minimizes the total code size (over all looped schedules that have F as the underlying firing sequence) using an efficient dynamic programming algorithm [30] called CDPPO. It is easily verified that the schedule  $S_2$  achieves the minimum total code size for the firing sequence  $S_1$  for any given values of  $\kappa(X)$ ,  $\kappa(Y)$ , and  $\kappa(Z)$ . In general, however, the set of looped schedules that minimize the code-size cost for a firing sequence may depend on the relative costs of the individual actors [30].

Schedules  $S_1$  and  $S_2$  both attain the minimum achievable buffer requirement of 11 for Fig. 12; however,  $S_2$  will generally achieve a much lower code-size cost. The code-size cost of  $S_2$  can be approximated as  $\kappa(X) + 2\kappa(Y) + 2\kappa(Z)$ . This approximation neglects the code-size overhead  $\lambda(S_2)$  of implementing the schedule loops (parenthesized terms) within  $S_2$ . In practice, this approximation rarely leads to misleading results. The looping overhead is typically very small compared to the code size saved by consolidating actor appearances in the schedule. This is especially true for the large number of DSP processors that employ so-called "zero-overhead looping" facilities [2]. Scheduling techniques that abandon this approximation, and incorporate looping overhead are examined in Section II-B-5.

It is possible to reduce the code-size cost below what is achievable by  $S_2$ ; however, this requires an increase in the buffering cost. For example, consider the schedule  $S_3 = X(10Y)(10Z)$ . Such a schedule is called a *single appearance schedule*, since it contains only one instantiation of each actor. Clearly (under the approximation of negligible looping overhead), any single appearance schedule gives a minimal code-size implementation of a DFG. However, a penalty in the buffer requirement must usually be paid for such code-size optimality.

For example, the code-size cost of  $S_3$  is  $(\kappa(X) + \kappa(Y))$  less than that of  $S_2$ ; however  $buf(S_3) = 25$ , while  $buf(S_2)$  is only

Beyond code-size optimality, another potentially important benefit of schedule  $S_3$  is that it minimizes the average rate at

which inter-actor context switching occurs. This schedule incurs three context switches (also called actor activations) per schedule period, while  $S_1$  and  $S_2$  both incur 21. Such minimization of context switching can significantly improve throughput and power consumption. The issue of context switching, and the systematic construction of minimum-context-switch schedules are discussed further in Section II-B-4.

An alternative single appearance schedule for Fig. 12 is  $S_4 = X(10YZ)$ . This schedule has the same optimal code-size cost as  $S_3$ . However, its buffer requirement of 16 is lower than that of  $S_3$ , since execution of actors Y and Z is fully interleaved, which limits data accumulation on the edge (Y, Z). This interleaving, however, brings the average rate of context switches to 21; and thus,  $S_3$  is clearly advantageous in terms of this metric.

In summary, there is a complex range of tradeoffs involved in synthesizing an application program from a dataflow specification. This is true even when we restrict ourselves to inline implementations, which entirely avoid the (call/return/parameter passing) overhead of subroutines. In the remainder of this section, we review a number of techniques that have been developed for addressing some of these complex tradeoffs. Sections II-B-3 and II-B-4 focus primarily on inline implementations. In Section II-B-5, we examine some recently developed techniques that have been developed to incorporate subroutine-based threading into the design space.

3) Minimization of Memory Requirements: Minimizing program and data memory requirements is critical in many embedded DSP applications. On-chip memory capacities are limited, and the speed, power, and financial cost penalties of employing off-chip memory may be prohibitive or highly undesirable. Three general avenues have been investigated for minimizing memory requirements: 1) minimization of the buffer requirement, which usually forms a significant component of the overall data space cost; 2) minimization of code size; and 3) joint exploration of the tradeoff involving code size and buffer requirements.

It has been shown that the problem of constructing a schedule that minimizes the buffer requirement over all valid schedules is NP-complete [11]. Thus, for practical scalable algorithms, we must resort to heuristics. Ade [31] has developed techniques for computing tight lower bounds on the buffer requirement for a number of restricted subclasses of delayless, acyclic graphs, including arbitrary-length chain-structured graphs. Some of these bounds have been generalized to handle delays in [11]. Approximate lower bounds for general graphs are derived in [32]. Cubric and Panangaden have presented an algorithm that achieves optimum buffer requirements for acyclic SDF graphs that may have one or more independent, undirected cycles [33]. An effective heuristic for general graphs, which is employed in the Gabriel [14] and Ptolemy [7] systems, is given in [11]. Govindarajan et al. have developed an SDF buffer-minimization algorithm for multiprocessor implementation [34]. This algorithm minimizes the buffer memory cost over all multiprocessor schedules that have optimal throughput.

For complex multirate applications—which are the most challenging for memory management—the structure of minimum buffer schedules is, in general, highly irregular [35], [11]. Such schedules offer relatively few opportunities to organize

compact loop structures, and thus have very high code-size costs under inlined implementations. Thus, such schedules are often not useful, even though they may achieve very low buffer requirements. Schedules at the extreme of minimum code size, on the other hand, typically exhibit a much more favorable trade-off between code and buffer memory costs [36].

These empirical observations motivate the problem of code-size minimization. A central goal when attempting to minimize code size for inlined implementations is that of constructing a single appearance schedule whenever one exists. A valid single appearance schedule exists for any consistent, acyclic SDF graph. Furthermore, a valid single appearance schedule can be derived easily from any topological sort (a topological sort of a directed acyclic graph G is a linear ordering of all its vertices such that for each edge (x, y) in G, x appears before y in the ordering) of an acyclic graph G: if  $(A_1, A_2, \ldots, A_m)$  is a topological sort of G, then it is easily seen that the single appearance schedule  $(q(A_1)A_1)(q(A_2)A_2)\dots(q(A_m)A_m)$  is valid. For a cyclic graph, a single appearance schedule may or may not exist, depending on the location and magnitude of delays in the graph. An efficient strategy, called the loose interdependence algorithm framework (LIAF), has been developed that constructs a single appearance schedule whenever one exists [37]. Furthermore, for general graphs, this approach guarantees that all actors that are not contained in a certain type of subgraph, called tightly interdependent subgraphs, will have only one appearance in the generated schedule [38]. In practice, tightly interdependent subgraphs arise only very rarely, and thus, the LIAF technique guarantees full code-size optimality for most applications. Because of its flexibility and provable performance, the LIAF is employed in a number of widely used tools, including Ptolemy and Cadence's SPW.

The LIAF constructs a single appearance schedule by decomposing the input graph into a hierarchy of acyclic subgraphs, which correspond to an outer-level hierarchy of nested loops in the generated schedule. The acyclic subgraphs in the hierarchy can be scheduled with any existing algorithm that constructs single appearance schedules for acyclic graphs. The particular algorithm that is used in a given implementation of the LIAF is called the acyclic scheduling algorithm. For example, the topological-sort-based approach described above could be used as the acyclic scheduling algorithm. However, this simple approach has been shown to lead to relatively large buffer requirements [11]. This motivates a key problem in the joint minimization of code and data for SDF specifications. This is the problem of constructing a single appearance schedule for an acyclic SDF graph that minimizes the buffer requirement over all valid single appearance schedules. Since any topological sort leads to a distinct schedule for an acyclic graph, and the number of topological sorts is not polynomially bounded in the graph size, exhaustive evaluation of single appearance schedules is not tractable. Thus, as with the (arbitrary appearance) buffer minimization problem, heuristics have been explored. Two complementary, low-complexity heuristics, called APGAN [39] and RPMC [40], have proven to be effective on practical applications when both are applied, and the best resulting schedule is selected. Furthermore, it has been formally shown that APGAN gives optimal

Fig. 13. Example that we use to illustrate the  $N_{\rm act}$  metric.

results for a broad class of SDF systems. Thorough descriptions of APGAN, RPMC, and the LIAF, and their inter-relationships can be found in [11], [36]. A scheduling framework for applying these techniques to multiprocessor implementations is described in [41]. Recently developed techniques for efficient sharing of memory among multiple buffers from a single appearance schedule are developed in [42]–[44].

Although APGAN and RPMC provide good performance on many applications, these heuristics can sometimes produce results that are far from optimal [45]. Furthermore, as discussed in Section I, DSP software tools are allowed to spend more time for optimization of code than what is required by low-complexity, deterministic algorithms such as APGAN and RPMC. Motivated by these observations, Zitzler, Teich, and Bhattacharyya have developed an effective stochastic optimization approach, called GASAS, for constructing minimum-buffer single appearance schedules [46], [47]. The GASAS approach is based on a genetic algorithm [48] formulation in which topological sorts are encoded as "chromosomes," which randomly "mutate" and "recombine" to explore the search space. Each topological sort in the evolution is optimized by the efficient local search algorithm CDPPO [30], which was mentioned earlier in Section II-B-2. Using dynamic programming, CDPPO computes a minimum memory single appearance schedule for a given topological sort. To exploit the valuable optimality property of APGAN whenever it applies, the solution generated by APGAN is included in the initial population, and an elitist evolution policy is enforced to ensure that the fittest individual always survives to the next generation.

4) Throughput Optimization: At the Aachen University of Technology, as part of the COSSAP design environment (now developed by Synopsys) project, Ritz, Pankert, and Meyr have investigated the minimization of the context-switch overhead, or the average rate at which actor activations occur [20]. As discussed in Section II-B-2, an actor activation occurs whenever two distinct actors are invoked in succession; for example, the schedule (2(2B)(5A))(5C) for Fig. 13 results in five activations per schedule period.

Activation overhead includes saving the contents of registers that are used by the next actor to invoke, if necessary, and loading state variables and buffer pointers into registers. The concept of grouping multiple invocations of the same actor together to reduce context-switch overhead is referred to as *vectorization*. The SSDF model, discussed in Section II-A-6, allows the benefits of vectorization to extend beyond the actor interface level (inter-actor context switching). For example, con-

Fig. 14. Example illustrates that minimizing actor activations does not imply minimizing actor appearances.

text switching between successive sub-functions of a complex actor can be amortized over  $N_v$  invocations of the sub-functions, where  $N_v$  is the given vectorization parameter.

Ritz estimates the average rate of activations for a periodic schedule S as the number of activations that occur in one iteration of S divided by the blocking factor of S. This quantity is denoted by  $N_{\rm act}(S)$  For example, for Fig. 13,  $N_{\rm act}((2(2B)(5A))(5C))=5$  and  $N_{\rm act}((4(2B)(5A))(10C))=9/2=4.5$ . If, for each actor, each invocation takes the same amount of time, and if we ignore the time spent on computation that is not directly associated with actor invocations (for example, schedule loops), then  $N_{\rm act}(S)$  is directly proportional to the number of actor activations per unit time. For consistent acyclic SDF graphs,  $N_{\rm act}$  clearly can be made arbitrarily large by increasing the blocking factor sufficiently; thus, as with the problem of constructing compact schedules, the extent to which the activation rate can be minimized is limited by the cyclic regions in the input SDF specification.

The technique developed in [20] attempts to find a valid single appearance schedule that minimizes  $N_{\rm act}$  over all valid single appearance schedules. Note that minimizing the number of activations does not imply minimizing the number of appearances. As a simple example, consider the SDF graph in Fig. 14. It can be verified that for this graph, the lowest value of  $N_{\rm act}$  that is obtainable by a valid single appearance schedule is 0.75, and one valid single appearance schedule that achieves this minimum rate is (4B)(4A)(4C). However, valid schedules exist that are not single appearance schedules, and that have values of  $N_{\rm act}$  below 0.75; for example, the valid schedule (4B)(4A)(3B)(3A)(7C) contains two appearances each of A and B, and satisfies  $N_{\rm act} = 5/7 = 0.71$ .

Thus, since Ritz's vectorization approach focuses on single appearance schedules, the primary objective of the techniques in [20] is implicitly code-size minimization. This is reasonable since in practice, code size is often of critical concern. The overall objective in [20] is to construct a minimum activation implementation over all implementations that have minimum code size.

Ritz defines the *relative vectorization degree* of a simple cycle (a cyclic path in the graph, in which no proper sub-path is cyclic) *C* in a consistent, connected SDF graph by

$$N_G(C)$$

$$= \max(\{\min(\{D_G(\beta)|\beta \in parallel(\alpha)\}) | \alpha \in edges(C)\})$$

$^1\mathrm{Every}$  periodic schedule invokes each actor A some multiple of q(A) times. This multiple, denoted by J, is called the blocking factor. A minimal periodic schedule is one that satisfies J=1. For memory minimization, there is no penalty in restricting consideration to minimal schedules [11]. When attempting to minimize  $N_{\mathrm{act}}$ , however, it is in general advantageous to consider J>1.

Fig. 15. Illustration of a complete hierarchization.

where

$$D_G(\alpha) = \left\lfloor \frac{del(\alpha)}{q(src(\alpha))prd(\alpha)} \right\rfloor$$

(9)

is the delay on edge  $\alpha$ , normalized by the total number of tokens exchanged on  $\alpha$  in a minimal schedule period of G, and

$$parallel(\alpha) = \{ \beta \in edges(G) | (src(\beta) = src(\alpha))$$

and  $(snk(\beta) = snk(\alpha)) \}$

is the set of edges with the same source and sink as  $\alpha$ . Here, edges(G) simply denotes the set of edges in the SDF graph G.

For example, if G denotes the SDF graph in Fig. 13, and  $\chi$  denotes the cycle in G whose associated graph contains the actors A and B, then  $D_G(\chi) = \lfloor 10/20 \rfloor = 0$ ; and if G denotes the graph in Fig. 14 and  $\chi$  denotes the cycle whose associated graph contains A and C, then  $D_G(\chi) = \lceil 7/1 \rceil = 7$ .

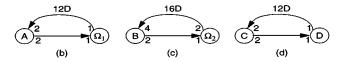

Ritz et al. postulate that given a strongly connected SDF graph, a valid single appearance schedule that minimizes  $N_{\rm act}$ can be constructed from a complete hierarchization, which is a cluster hierarchy such that only connected subgraphs are clustered, all cycles at a given level of the hierarchy have the same relative vectorization degree, and cycles in higher levels of the hierarchy have strictly higher relative vectorization degrees than cycles in lower levels. Fig. 15 depicts a complete hierarchization of an SDF graph. Fig. 15(a) shows the original SDF graph; here q(A, B, C, D) = (1, 2, 4, 8). Fig. 15(b) shows the top level of the cluster hierarchy. The hierarchical actor  $\Omega_1$  represents  $subgraph(\{B, C, D\})$ , and this subgraph is decomposed as shown in Fig. 15(c), which gives the next level of the cluster hierarchy. Finally, Fig. 15(d) shows that  $subgraph(\{C, D\})$  corresponds to  $\Omega_2$  and is the bottom level of the cluster hierarchy.

Now observe that the relative vectorization degree of the fundamental cycle in Fig. 15(c) with respect to the original SDF graph is  $\lfloor 16/8 \rfloor = 2$ , while the relative vectorization degree of the fundamental cycle in Fig. 15(b) is  $\lfloor 12/2 \rfloor = 6$ ; and the relative vectorization degree of the fundamental cycle in Fig. 15(c) is  $\lfloor 12/8 \rfloor = 1$ . We see that the relative vectorization degree decreases as we descend the hierarchy, and thus the hierarchization depicted in Fig. 15 is complete. The hierarchization step defined by each of the SDF graphs in Fig. 15(b)–(d) is called a *component* of the overall hierarchization.

Ritz's algorithm [20] constructs a complete hierarchization by first evaluating the relative vectorization degree of each fundamental cycle, determining the maximum vectorization degree, and then clustering the graphs associated with the fundamental cycles that do not achieve the maximum vectorization degree. This process is then repeated recursively on each of the clusters until no new clusters are produced. In general, this bottom-up construction process has unmanageable complexity. However, this normally does not create problems in practice, since the strongly connected components of useful signal processing systems are often small, particularly in large-grain descriptions. Details on Ritz's technique for translating a complete hierarchization into a hierarchy of nested loops can be found in [20]. A general optimal algorithm for vectorization of SSDF graphs based on the complete hierarchization concept discussed above is given in [20]. Joint minimization of vectorization and buffer memory cost is developed in [12], and adaptation of the retiming transformation to improve vectorization for SDF graphs is addressed in [49], [50].

5) Subroutine Insertion: The techniques discussed above assume a fixed-threading mode. In particular, they do not attempt to exploit the flexibility offered by hybrid threading. Sung et al. developed an approach that employs hybrid threading to share code among different actors that have similar functionality [51]. For example, an application may contain several FIR filter blocks that differ only in the number of taps and the set of filter coefficients. These are called different instances of a parameterized FIR module in the actor library. Sung's approach decomposes the code associated with an actor instance into the actor context and actor reference code, and carefully weighs the benefit of each code sharing opportunity with the associated overhead. The overhead stems from the actor context component, which includes instance-specific state variables and buffer pointers. Code must be inserted to manage this context so that each invocation of the shared code block (the "reference code") is appropriately customized to the associated instance.

Also, the GASAS framework has been significantly extended to consider multiple appearance schedules, and selectively apply hybrid threading to reduce the code-size cost of highly irregular schedules, which cannot be accommodated by compact loop structures [52]. Such irregularity often arises when exploring the space of schedules whose buffer requirements are significantly lower than what is achievable by single appearance schedules [11]. The objective of this genetic-algorithm-based exploration of hybrid threading and loop scheduling is to efficiently compute Pareto fronts in the multidimensional design evaluation space of program memory cost, buffer requirement, and execution time overhead.

The intelligent use of hybrid threading and code sharing (*sub-routine insertion optimizations*) can achieve lower code-size costs than what is achievable with single appearance schedules that use conventional inlining. If an inlined single appearance schedule fits within the available on-chip memory, it is not worth incurring the overhead of subroutine insertion. However, if an inline implementation is too large to be held on-chip, then subroutine insertion optimizations can eliminate, or greatly reduce the need for off-chip memory accesses. Since off-chip memory accesses involve significant execution time penalties, and large power consumption costs, subroutine insertion

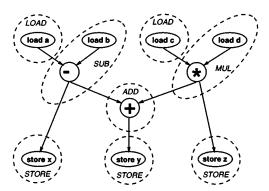

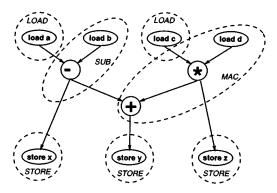

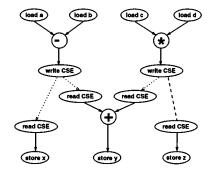

enables embedded software developers to exploit an important part of the overall design space.